# DIGITAL Semiconductor 21174 Core Logic Chip

# **Technical Reference Manual**

Order Number: EC-R12GC-TE

Revision/Update Information: This is a revised, preliminary

document. It supersedes the *DIGITAL Semiconductor 21174 Core Logic*

Chip Technical Reference Manual, EC-R12GB-TE.

# **Preliminary**

Digital Equipment Corporation Maynard, Massachusetts

http://www.digital.com/semiconductor

#### October 1997

While DIGITAL believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

©Digital Equipment Corporation 1997. All rights reserved. Printed in U.S.A.

DIGITAL, DIGITAL Semiconductor, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

DIGITAL Semiconductor is a Digital Equipment Corporation business.

Altera is a registered trademark of Altera Corporation.

Intel is a registered trademark of Intel Corporation.

NEC is a registered trademark of NEC Corporation.

Toshiba is a registered trademark of Kabushiki Kaisha Toshiba.

Windows NT is a trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective owners.

# Contents

# **Preface**

| I | Introduction          |                                              |              |  |  |

|---|-----------------------|----------------------------------------------|--------------|--|--|

|   | 1.1<br>1.2            | 21174 Features                               | 1–1<br>1–2   |  |  |

| 2 | Internal Architecture |                                              |              |  |  |

|   | 2.1<br>2.1.1          | Memory Controller                            | 2-1<br>2-1   |  |  |

|   | 2.1.2                 | DMA Read Transaction                         | 2-3          |  |  |

|   | 2.1.2.1<br>2.1.3      | PCI DMA Page Boundary Problem                | 2-3<br>2-4   |  |  |

|   | 2.1.3                 | 21174 DMA Lock Problem                       | 2-6          |  |  |

|   | 2.1.5                 | Minimum Memory Activation Period             | 2–6          |  |  |

|   | 2.2                   | Memory Banks                                 | 2-7          |  |  |

|   | 2.2.1                 | Refresh                                      | 2-7          |  |  |

|   | 2.2.2                 | Error Checking and Correction                | 2-7          |  |  |

|   | 2.2.3                 | DRAM Initialization                          | 2–8          |  |  |

|   | 2.3                   | PCI Interface                                | 2–9          |  |  |

|   | 2.3.1                 | Scatter-Gather Map                           | 2–9          |  |  |

|   | 2.3.2                 | DMA Read Prefetch                            | 2–9          |  |  |

|   | 2.3.3                 | DMA Write Buffer                             | 2–9          |  |  |

|   | 2.3.4                 | DMA Write Buffer Merging                     | 2–10         |  |  |

|   | 2.3.5                 | I/O Write Buffer                             | 2-10         |  |  |

|   | 2.3.6                 | Configuration Cycles and Special Cycles      | 2–10         |  |  |

|   | 2.4                   | Flash ROM Interface                          | 2–11         |  |  |

|   | 2.5                   | Auto DACK                                    | 2–12         |  |  |

|   | 2.6                   | Dummy Memory                                 | 2–12         |  |  |

|   | 2.7<br>2.8            | InterruptsGeneral-Purpose Inputs and Outputs | 2–13<br>2–14 |  |  |

|   | 2.9<br>2.10<br>2.10.1<br>2.10.2                             | Programmed 21164 Reset  Clock  Clock PLL  DRAM Clock Aligner                                                                                                                                                                           | 2–14<br>2–15<br>2–15<br>2–15                                |

|---|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 3 | Pinou                                                       | ıt                                                                                                                                                                                                                                     |                                                             |

|   | 3.1<br>3.2<br>3.3                                           | Pin List (Alphanumeric)                                                                                                                                                                                                                | 3–3<br>3–11<br>3–18                                         |

| 4 | Regis                                                       | ter Definitions                                                                                                                                                                                                                        |                                                             |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Register Types Register Addresses. General Registers Memory Controller Registers PCI Window Control Registers Scatter-Gather Address Translation Registers Miscellaneous Registers Interrupt Control Registers Flash ROM Address Space | 4-1<br>4-2<br>4-2<br>4-4<br>4-5<br>4-6<br>4-8<br>4-8<br>4-9 |

| 5 | Regis                                                       | ter Descriptions                                                                                                                                                                                                                       |                                                             |

|   | 5.1                                                         | Registers – General Description                                                                                                                                                                                                        | 5–1                                                         |

|   | 5.1.1                                                       | Revision Control Register (PYXIS_REV)                                                                                                                                                                                                  | 5–1                                                         |

|   | 5.1.2                                                       | PCI Latency Register (PCI_LAT)                                                                                                                                                                                                         | 5–2                                                         |

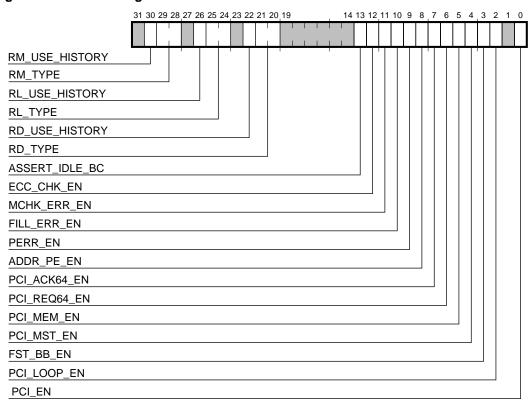

|   | 5.1.3                                                       | Control Register (PYXIS_CTRL)                                                                                                                                                                                                          | 5–4                                                         |

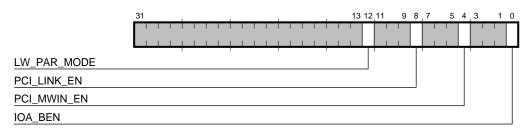

|   | 5.1.4                                                       | Control Register 1 (PYXIS_CTRL1)                                                                                                                                                                                                       | 5–7                                                         |

|   | 5.1.5                                                       | Flash Control Register (FLASH_CTRL)                                                                                                                                                                                                    | 5–8                                                         |

|   | 5.1.5.1                                                     | Calculating Flash ROM Access Time                                                                                                                                                                                                      | 5–10                                                        |

|   | 5.1.6                                                       | Hardware Address Extension Register (HAE_MEM)                                                                                                                                                                                          | 5–11<br>5–12                                                |

|   | 5.1.7<br>5.1.8                                              | Hardware Address Extension Register (HAE_IO)                                                                                                                                                                                           | 5–12<br>5–13                                                |

|   | 5.1.6                                                       | Diagnostic Register Descriptions                                                                                                                                                                                                       | 5–13                                                        |

|   | 5.2.1                                                       | Diagnostic Control Register (PYXIS_DIAG)                                                                                                                                                                                               | 5–14                                                        |

|   | 5.2.2                                                       | Diagnostic Check Register (DIAG_CHECK)                                                                                                                                                                                                 | 5–15                                                        |

|   | 5.3                                                         | Performance Monitor Register Descriptions                                                                                                                                                                                              | 5–15                                                        |

|   | 5.3.1                                                       | Performance Monitor Register (PERF_MONITOR)                                                                                                                                                                                            | 5–16                                                        |

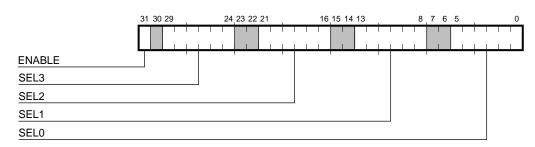

|   | 5.3.2                                                       | Performance Monitor Control Register (PERF_CONTROL)                                                                                                                                                                                    | 5–16                                                        |

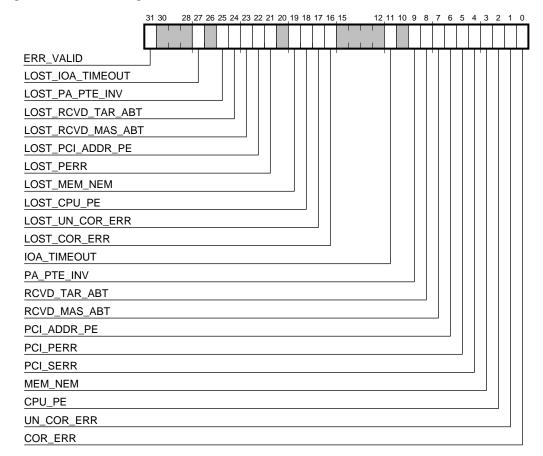

|   | 5.4                                                         | Error Register Descriptions                                                                                                                                                                                                            | 5–19                                                        |

|   | 5.4.1                                                       | Error Register (PYXIS_ERR)                                                                                                                                                                                                             | 5–19                                                        |

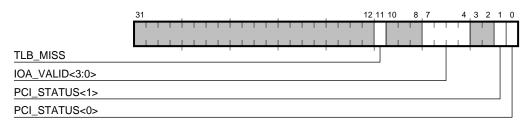

| 5.4.2   | Status Register (PYXIS_STAT)                                 | 5-22 |

|---------|--------------------------------------------------------------|------|

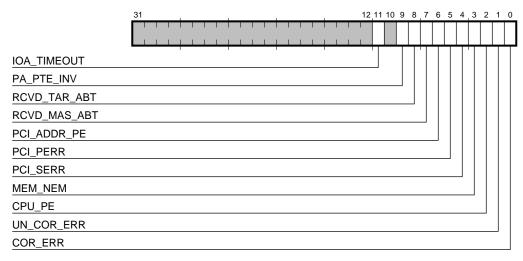

| 5.4.3   | Error Mask Register (ERR_MASK)                               | 5-23 |

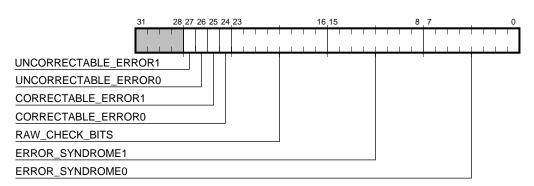

| 5.4.4   | Syndrome Register (PYXIS_SYN)                                | 5–24 |

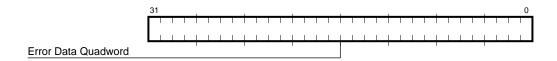

| 5.4.5   | Error Data Register (PYXIS_ERR_DATA)                         | 5-26 |

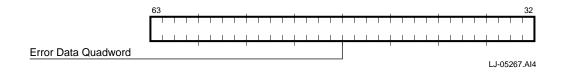

| 5.4.6   | Memory Error Address Register (MEAR)                         | 5-26 |

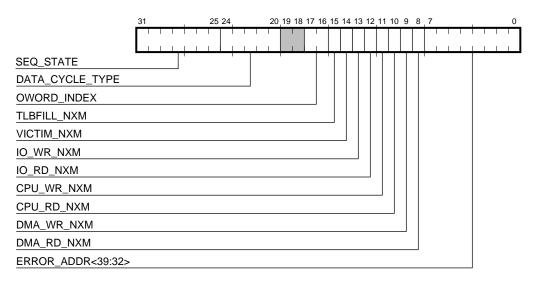

| 5.4.7   | Memory Error Status Register (MESR)                          | 5-27 |

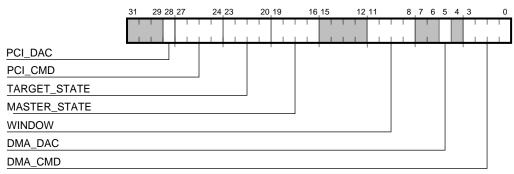

| 5.4.8   | PCI Error Register 0 (PCI_ERR0)                              | 5-33 |

| 5.4.9   | PCI Error Register 1 (PCI_ERR1)                              | 5-35 |

| 5.4.10  | PCI Error Register 2 (PCI_ERR2)                              | 5-36 |

| 5.5     | Memory Controller Register Descriptions                      | 5-37 |

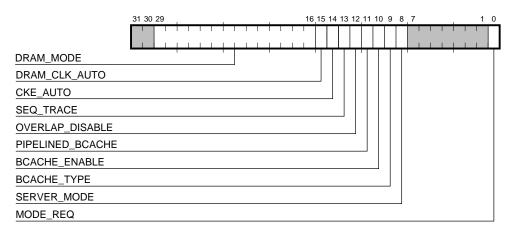

| 5.5.1   | Memory Control Register (MCR)                                | 5-38 |

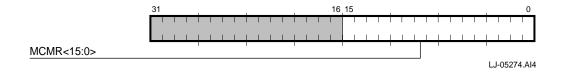

| 5.5.2   | Memory Clock Mask Register (MCMR)                            | 5-41 |

| 5.5.3   | Global Timing Register (GTR)                                 | 5-42 |

| 5.5.4   | Refresh Timing Register (RTR)                                | 5-44 |

| 5.5.5   | Row History Policy Mask Register (RHPR)                      | 5-45 |

| 5.5.6   | Memory Control Debug Register 1 (MDR1)                       | 5-46 |

| 5.5.7   | Memory Control Debug Register 2 (MDR2)                       | 5-47 |

| 5.5.8   | Base Address Registers (BBAR0–BBAR7)                         | 5-48 |

| 5.5.9   | Bank Configuration Registers (BCR0–BCR7)                     | 5-49 |

| 5.5.10  | Bank Timing Registers (BTR0-BTR7)                            | 5–51 |

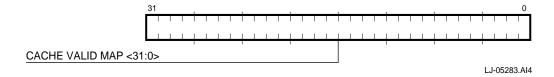

| 5.5.11  | Cache Valid Map Register (CVM)                               | 5-52 |

| 5.6     | PCI Window Control Register Descriptions                     | 5-53 |

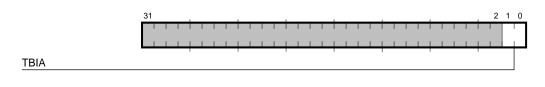

| 5.6.1   | Scatter-Gather Translation Buffer Invalidate Register (TBIA) | 5-53 |

| 5.6.1.1 | Preventing 21174 Hang when TBIA=3                            | 5-54 |

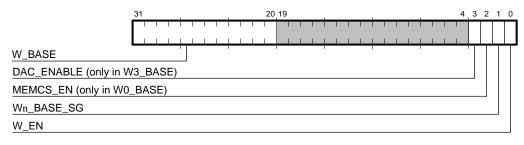

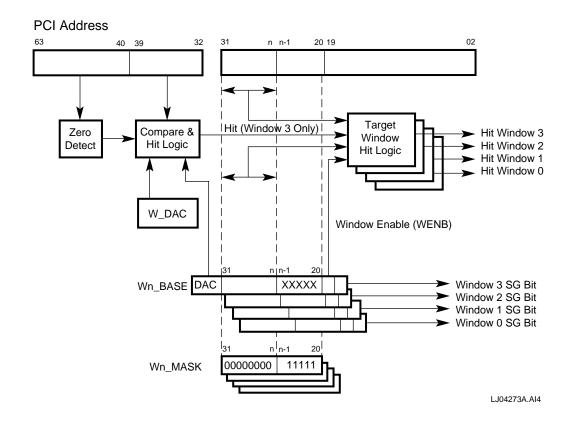

| 5.6.2   | Window Base Registers (Wn_BASE, n=0-3)                       | 5–55 |

| 5.6.2.1 | Determining a Hit in the Target Window                       | 5–56 |

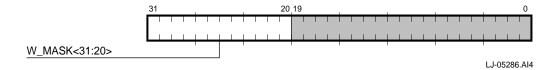

| 5.6.3   | Window Mask Registers (Wn_MASK, n=0-3)                       | 5–57 |

| 5.6.3.1 | Determining a Hit in the Target Window                       | 5–57 |

| 5.6.4   | Translated Base Registers (Tn_BASE, n=0-3)                   | 5-60 |

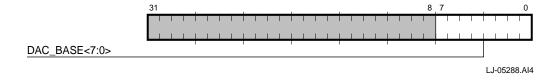

| 5.6.5   | Window DAC Base Register (W_DAC)                             | 5-61 |

| 5.7     | Scatter-Gather Address Translation Register Descriptions     | 5-62 |

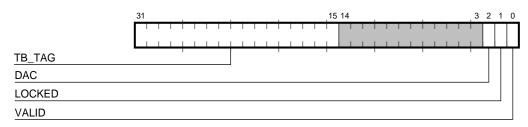

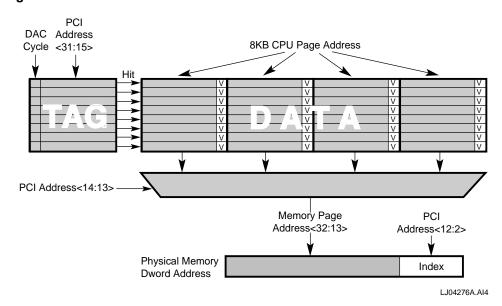

| 5.7.1   | Lockable Translation Buffer Tag Registers (LTB_TAGn, n=0-3)  | 5–62 |

| 5.7.1.1 | Determining a Hit in the Translation Buffer                  | 5-63 |

| 5.7.1.2 | Operation on a SG_TLB Miss                                   | 5-63 |

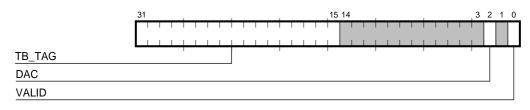

| 5.7.2   | Translation Buffer Tag Registers (TB_TAGn, n=4-7)            | 5-64 |

| 5.7.2.1 | Determining a Hit in the Translation Buffer                  | 5-65 |

| 5.7.2.2 | Operation on a SG_TLB Miss                                   | 5-65 |

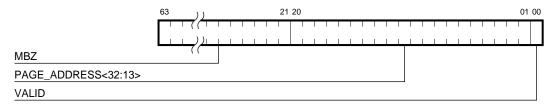

| 5.7.3   | Translation Buffer Page Registers (TBm_PAGEn, m=0-7, n=0-3)  | 5-65 |

| 5.7.3.1 | Determining a Hit in the Translation Buffer                  | 5-66 |

| 5.8     | Miscellaneous Register Descriptions                          | 5-66 |

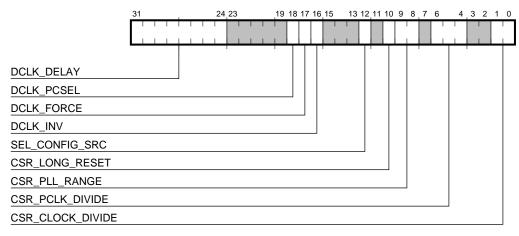

| 5.8.1   | Clock Control Register (CCR)                                 | 5-67 |

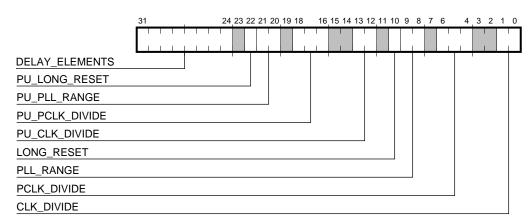

| 5.8.2   | Clock Status Register (CLK_STAT)                             | 5–69 |

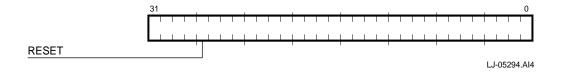

| 5.8.3   | Reset Register (RESET)                                       | 5–71 |

| 5.9     | Interrupt Control Registers Descriptions                     | 5–72 |

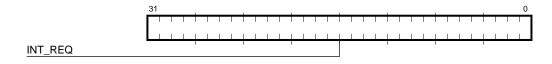

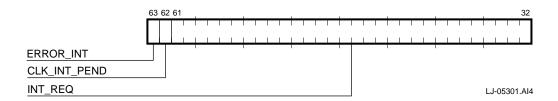

| 5.9.1   | Interrupt Request Register (INT_REQ)                         | 5–72 |

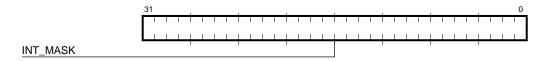

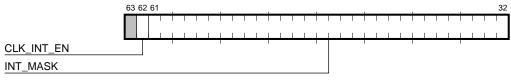

| 5.9.2   | Interrupt Mask Register (INT_MASK)                           | 5–73 |

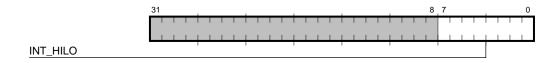

| 5.9.3   | Interrupt High/Low Select Register (INT_HILO)                | 5–74 |

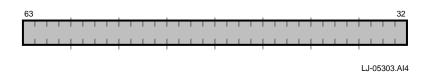

|   | 5.9.4  | Interrupt Routine Select Register (INT_ROUTE)                        | 5–7 |

|---|--------|----------------------------------------------------------------------|-----|

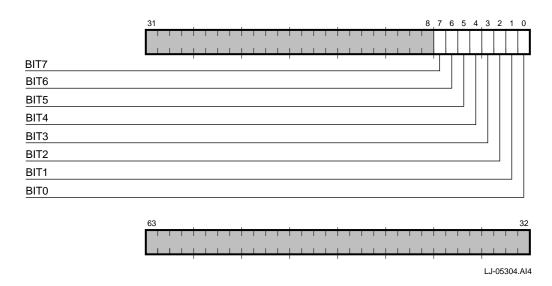

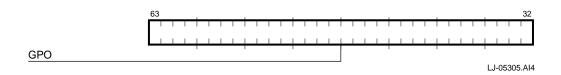

|   | 5.9.5  | General-Purpose Output Register (GPO)                                | 5-7 |

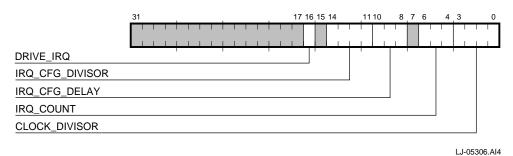

|   | 5.9.6  | Interrupt Configuration Register (INT_CNFG)                          | 5-7 |

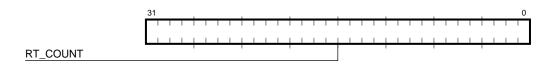

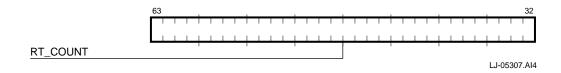

|   | 5.9.7  | Real-Time Counter Register (RT_COUNT)                                | 5–8 |

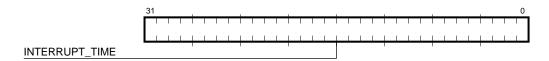

|   | 5.9.8  | Interrupt Time Register (INT_TIME)                                   | 5–8 |

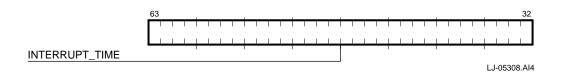

|   | 5.9.9  | I2C Control Register (IIC_CTRL)                                      | 5–8 |

|   |        |                                                                      |     |

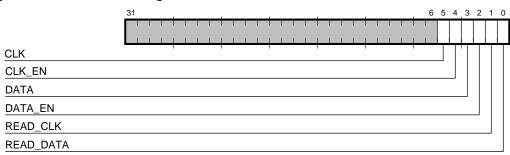

| 6 | Systo  | m Address Space                                                      |     |

| J | Syste  | in Address Space                                                     |     |

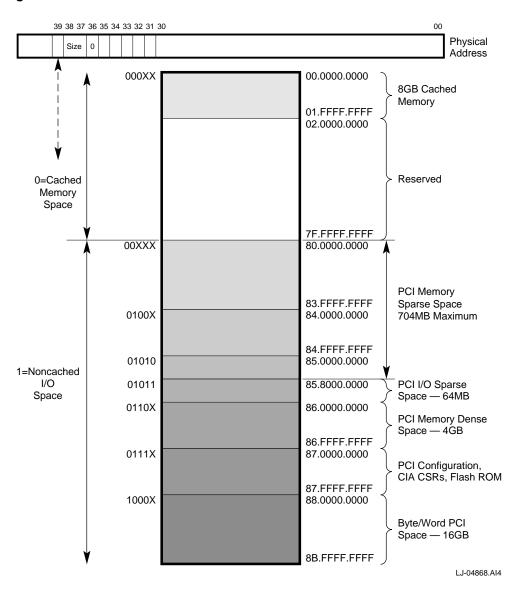

|   | 6.1    | Address Map                                                          | 6-  |

|   | 6.2    | PCI Address Space                                                    | 6-  |

|   | 6.3    | 21164 Address Space                                                  | 6-  |

|   | 6.3.1  | System Address Map                                                   | 6–  |

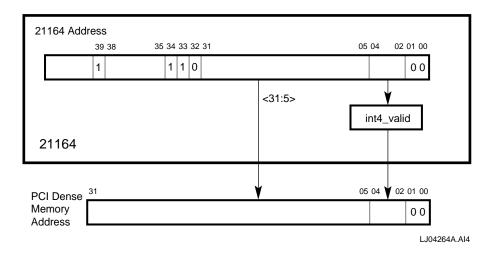

|   | 6.4    | 21164 Byte/Word PCI Space                                            | 6–  |

|   | 6.4.1  | 21164 Size Field                                                     | 6-  |

|   | 6.5    | Cacheable Memory Space                                               | 6-  |

|   | 6.6    | PCI Dense Memory Space                                               | 6-  |

|   | 6.7    | PCI Sparse Memory Space                                              | 6-  |

|   | 6.7.1  | Hardware Extension Register (HAE_MEM)                                | 6-  |

|   | 6.7.2  | Memory Access Rules and Operation                                    | 6-  |

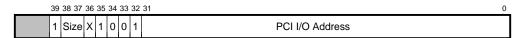

|   | 6.8    | PCI Sparse I/O Space                                                 | 6-  |

|   | 6.8.1  | Hardware Extension Register (HAE_IO)                                 | 6-  |

|   | 6.8.2  | PCI Sparse I/O Space Access Operation                                | 6-  |

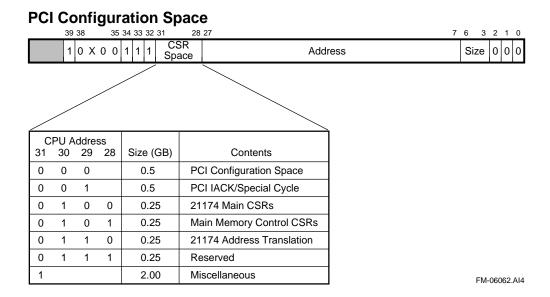

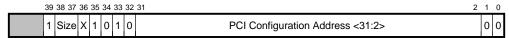

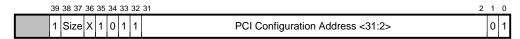

|   | 6.9    | PCI Configuration Space                                              | 6-  |

|   | 6.10   | PCI Special/Interrupt Cycles                                         | 6-  |

|   | 6.11   | Hardware-Specific and Miscellaneous Register Space                   | 6-  |

|   | 6.12   | PCI to Physical Memory Address                                       | 6-  |

|   | 6.13   | Direct-Mapped Addressing                                             | 6-  |

|   | 6.14   | Scatter-Gather Addressing                                            | 6-  |

|   | 6.15   | Scatter-Gather TLB                                                   | 6-  |

|   | 6.15.1 | Scatter-Gather TLB Hit Process                                       | 6-  |

|   | 6.15.2 | Scatter-Gather TLB Miss Process                                      | 6-  |

|   | 6.16   | Suggested Use of a PCI Window                                        | 6-  |

|   | 6.16.1 | Peripheral Component Architecture Compatibility Addressing and Holes | 6-  |

|   | 6.16.2 | Memory Chip Select Signal mem_cs_I                                   | 6-  |

|   |        |                                                                      |     |

| 7 | Electr | rical Specifications                                                 |     |

|   | 7.1    | PCI Electrical Specification Conformance                             | 7   |

|   | 7.1    | Absolute Maximum Ratings                                             | 7   |

|   | 7.3    | DC Specifications                                                    | 7-  |

|   | 1.5    | DO Opcomodiono                                                       | ,   |

| 8                         | Mechanical and Thermal Specifications                       |                                                                                                                                                                                                              |                                                      |  |  |  |

|---------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

|                           | 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.3.1<br>8.2.3.2 | Mechanical Specifications. Thermal Specifications Operating Temperature Thermal Design Recommendations. Heat Sinks Clip-on Heat Sink Assembly Tape Heat Sink Assembly                                        | 8–1<br>8–4<br>8–4<br>8–4<br>8–5<br>8–6               |  |  |  |

| Α                         | 2117                                                        | 4 DMA Page Boundary Solution                                                                                                                                                                                 |                                                      |  |  |  |

|                           | A.1<br>A.2<br>A.2.1                                         | Read Page Problem                                                                                                                                                                                            | A-1<br>A-1<br>A-1                                    |  |  |  |

| B 21174 DMA Lock Solution |                                                             | 4 DMA Lock Solution                                                                                                                                                                                          |                                                      |  |  |  |

|                           | B.1<br>B.2                                                  | DMA Lock Problem                                                                                                                                                                                             | B–1<br>B–1                                           |  |  |  |

| С                         | Alpha                                                       | aPC 164LX Layout Design Rules                                                                                                                                                                                |                                                      |  |  |  |

|                           | C.1<br>C.2<br>C.3<br>C.4<br>C.4.1<br>C.4.2<br>C.5           | Application Note AlphaPC 164LX Layer Construction Bcache Signal Layout Lengths 21174 Clock Layout DRAM Clock Signal Layout Rules PCI Clock Signal Layout Rules Bcache Signal Layout Rules PCI General Layout | C-1<br>C-3<br>C-5<br>C-6<br>C-6<br>C-6<br>C-7<br>C-8 |  |  |  |

**Support, Products, and Documentation**

# **Figures**

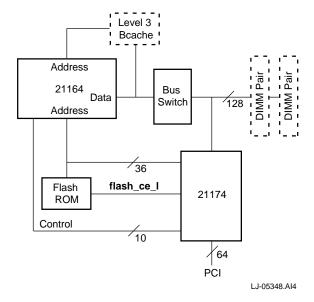

| 1–1  | System Configuration                                  | 1–2  |

|------|-------------------------------------------------------|------|

| 2–1  | 21174 Block Diagram                                   | 2–2  |

| 2–2  | DMA Read Transaction Flow Diagram                     | 2–4  |

| 2–3  | DMA Write Transaction Flow Diagram                    | 2–5  |

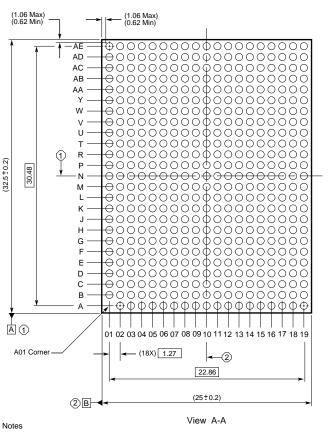

| 3–1  | 21174 BGA Pin Assignment (Pads Down)                  | 3–2  |

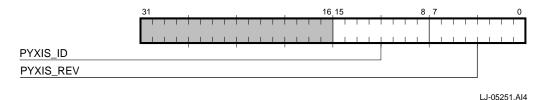

| 5–1  | Revision Control Register                             | 5–1  |

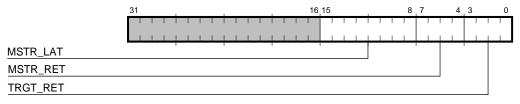

| 5–2  | PCI Latency Register                                  | 5–2  |

| 5–3  | Control Register                                      | 5–4  |

| 5–4  | Control Register 1                                    | 5–7  |

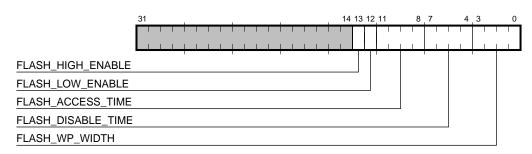

| 5–5  | Flash Control Register                                | 5–9  |

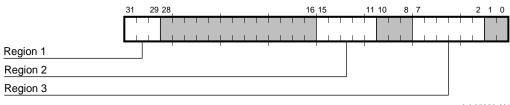

| 5–6  | Hardware Address Extension Register (HAE_MEM)         | 5–11 |

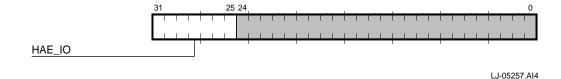

| 5–7  | Hardware Address Extension Register (HAE_IO)          | 5–12 |

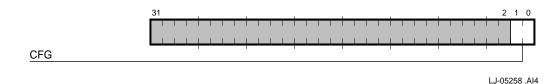

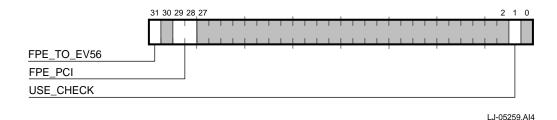

| 5–8  | Configuration Type Register                           | 5–13 |

| 5–9  | Diagnostic Control Register                           | 5–14 |

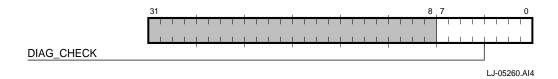

| 5-10 | Diagnostic Check Register                             | 5–15 |

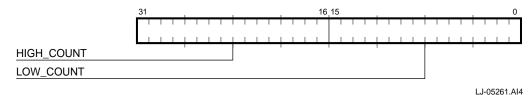

| 5-11 | Performance Monitor Register                          | 5–16 |

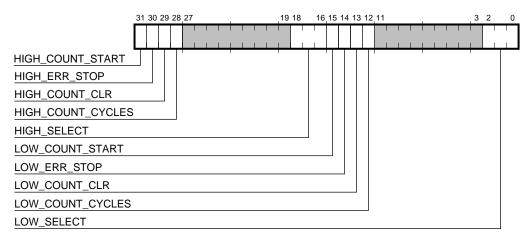

| 5-12 | Performance Monitor Control Register                  | 5–17 |

| 5-13 | Error Register                                        | 5–19 |

| 5-14 | Status Register                                       | 5-22 |

| 5-15 | Error Mask Register                                   | 5-23 |

| 5-16 | Syndrome Register                                     | 5-25 |

| 5-17 | Error Data Register                                   | 5-26 |

| 5-18 | Memory Error Address Register                         | 5-27 |

| 5-19 | Memory Error Status Register                          | 5–28 |

| 5-20 | PCI Error Register 0                                  | 5-33 |

| 5-21 | PCI Error Register 1                                  | 5-36 |

| 5-22 | PCI Error Register 2                                  | 5–37 |

| 5-23 | Memory Control Register                               | 5-38 |

| 5-24 | Memory Clock Mask Register                            | 5-41 |

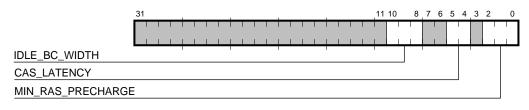

| 5-25 | Global Timing Register                                | 5-43 |

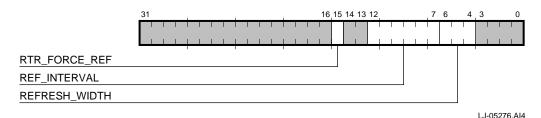

| 5-26 | Refresh Timing Register                               | 5-44 |

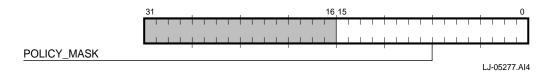

| 5-27 | Row History Policy Mask Register                      | 5-45 |

| 5-28 | Memory Control Debug Register 1                       | 5-46 |

| 5-29 | Memory Control Debug Register 2                       | 5–47 |

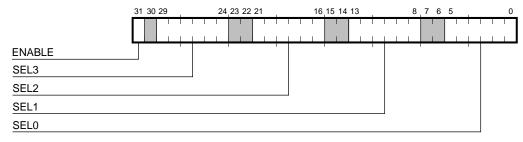

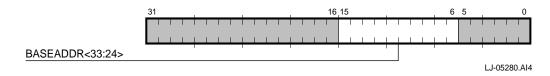

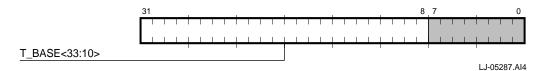

| 5-30 | Base Address Register                                 | 5-48 |

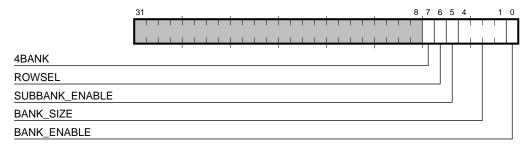

| 5-31 | Bank Configuration Register                           | 5-49 |

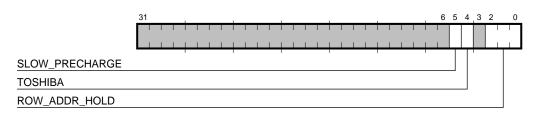

| 5-32 | Bank Timing Register                                  | 5–51 |

| 5-33 | Cache Valid Map Register                              | 5-52 |

| 5–34 | Scatter-Gather Translation Buffer Invalidate Register | 5–54 |

| 5–35 | Window Base Register                                  | 5–55 |

| 5–36 | Window Mask Register                                  | 5–57 |

|      |                                                       |      |

| 5–37 | Translated Base Register                                         | 5–60 |

|------|------------------------------------------------------------------|------|

| 5-38 | Window DAC Base Register                                         | 5-61 |

| 5-39 | Lockable Translation Buffer Tag Register                         | 5-62 |

| 5-40 | Translation Buffer Tag Register                                  | 5-64 |

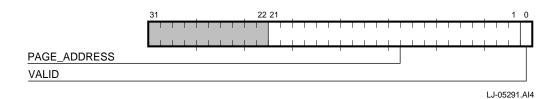

| 5-41 | Translation Buffer Page Register                                 | 5-66 |

| 5-42 | Clock Control Register                                           | 5-67 |

| 5-43 | Clock Status Register                                            | 5-69 |

| 5-44 | Reset Register                                                   | 5–71 |

| 5-45 | Interrupt Request Register                                       | 5-72 |

| 5-46 | Interrupt Mask Register                                          | 5-73 |

| 5-47 | Interrupt High/Low Select Register                               | 5–74 |

| 5-48 | Interrupt Routine Select Register                                | 5–75 |

| 5-49 | General-Purpose Output Register                                  | 5–77 |

| 5-50 | Interrupt Configuration Register                                 | 5–78 |

| 5-51 | Real-Time Counter Register                                       | 5-81 |

| 5-52 | Interrupt Time Register                                          | 5-82 |

| 5-53 | I2C Control Register                                             | 5–83 |

| 6–1  | Address Space Overview                                           | 6–5  |

| 6–2  | Memory Remapping                                                 | 6–6  |

| 6–3  | 21164 Address Space Configuration                                | 6–8  |

| 6–4  | 21164 and DMA Read and Write Transactions                        | 6–9  |

| 6–5  | System Address Map                                               | 6–11 |

| 6–6  | 21174 CSR Space                                                  | 6–12 |

| 6–7  | Byte/Word PCI Space                                              | 6–13 |

| 6–8  | Dense-Space Address Generation                                   | 6–17 |

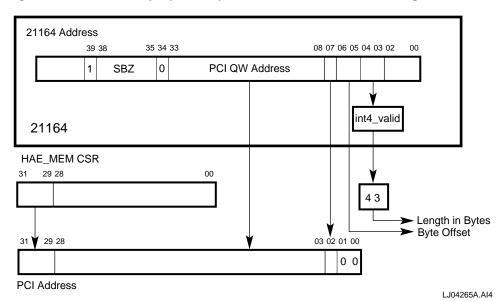

| 6–9  | PCI Memory Sparse-Space Address Generation – Region 1            | 6–21 |

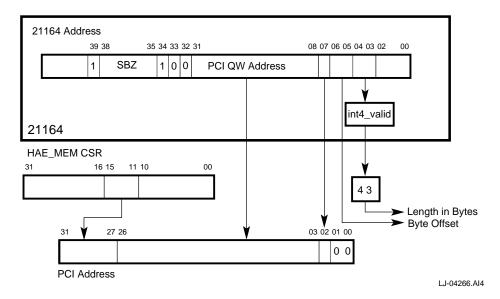

| 6–10 | PCI Memory Sparse-Space Address Generation – Region 2            | 6–22 |

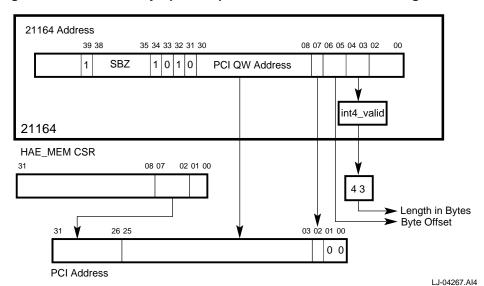

| 6–11 | PCI Memory Sparse-Space Address Generation – Region 3            | 6–22 |

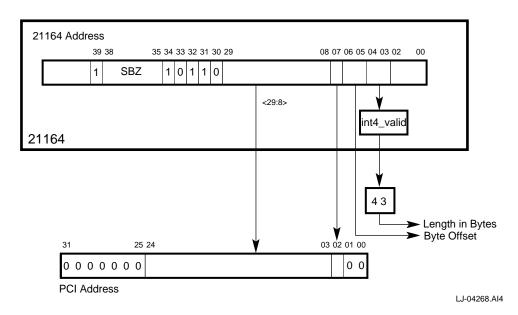

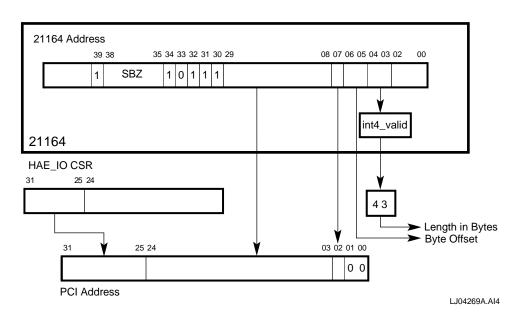

| 6–12 | PCI Sparse I/O Space Address Translation (Region A, Lower 32MB)  | 6–25 |

| 6–13 | PCI Sparse I/O Space Address Translation (Region B, Higher Area) | 6–25 |

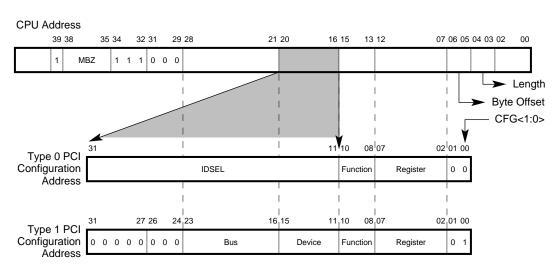

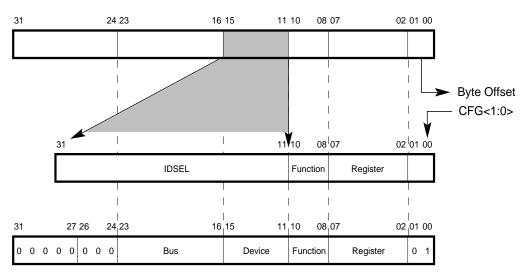

| 6–14 | PCI Configuration Space Definition (Sparse)                      | 6–27 |

| 6–15 | PCI Configuration Space Definition (Dense)                       | 6–27 |

| 6–16 | PCI Bus Hierarchy                                                | 6–30 |

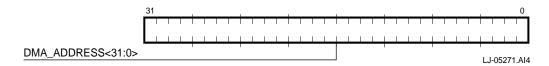

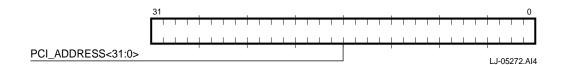

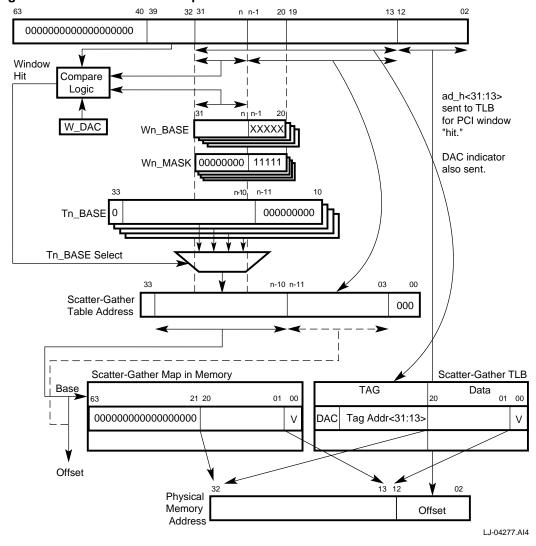

| 6–17 | PCI DMA Addressing Example                                       | 6–35 |

| 6–18 | PCI Target Window Compare                                        | 6–36 |

| 6–19 | Scatter-Gather PTE Format                                        | 6–39 |

| 6–20 | Scatter-Gather Associative TLB                                   | 6–41 |

| 6–21 | Scatter-Gather Map Translation                                   | 6–43 |

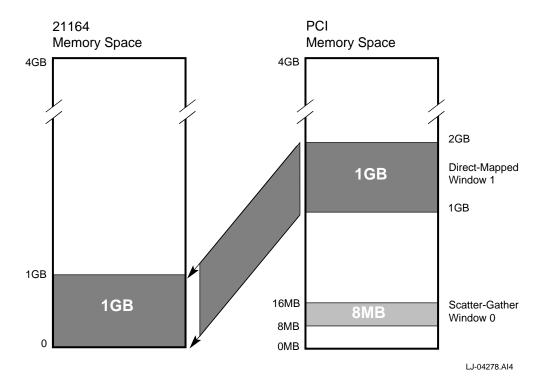

| 6–22 | Default PCI Window Allocation.                                   | 6–44 |

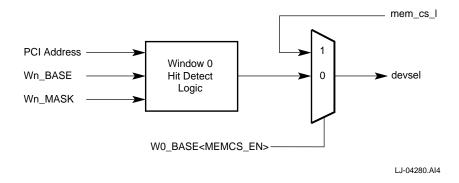

| 6–23 | mem_cs_l Decode Area                                             | 6–46 |

| 6–24 | mem_cs_l Logic                                                   | 6–47 |

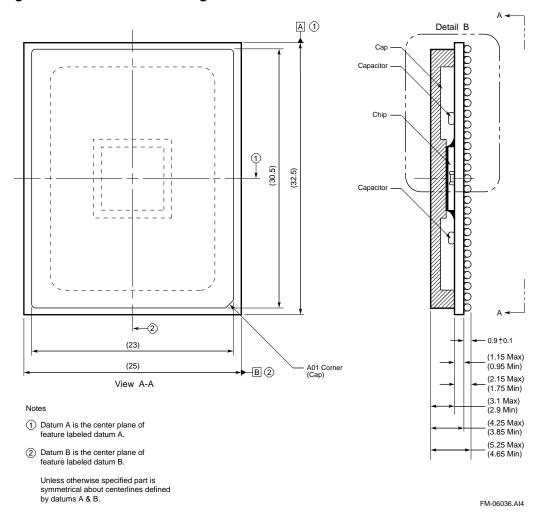

| 8–1  | 474-Pin BGA Package                                              | 8–2  |

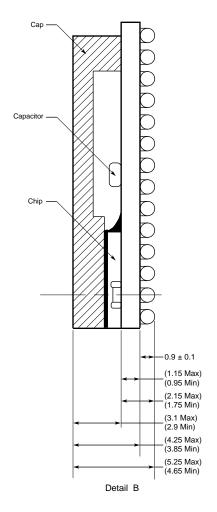

| 8–2  | 21174 Physical Specification                                     | 8–3  |

|      |                                                                  | 5 5  |

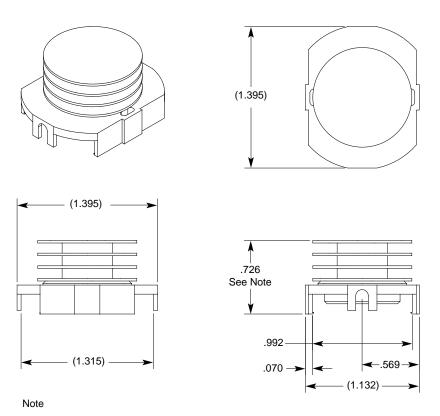

| 8–3 | Clip-on Heat Sink Assembly | 8–5 |

|-----|----------------------------|-----|

| 8–4 | Tape Heat Sink Assembly    | 8–6 |

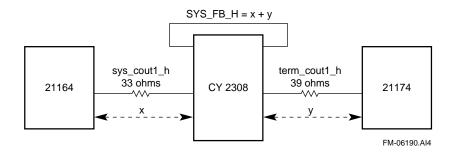

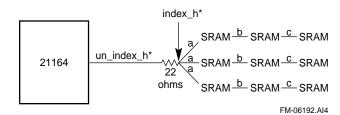

| C-1 | sys_cout1_h Layout         |     |

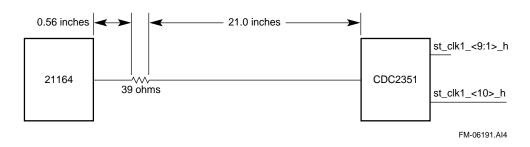

| C-2 | st_clk1_h Layout.          | C-5 |

| C-3 | Bcache Signal Layout       | C-7 |

| C-4 | Beache Signal Layout       | C-8 |

# **Tables**

| 1    | Data Units                                                | xvi   |  |  |  |  |

|------|-----------------------------------------------------------|-------|--|--|--|--|

| 2    | Register Field Notation                                   | xviii |  |  |  |  |

| 3    | Unnamed Register Field Notation                           |       |  |  |  |  |

| 2-1  | PCI Operating Frequencies                                 |       |  |  |  |  |

| 2-2  | Flash ROM Pin Assignment                                  | 2-11  |  |  |  |  |

| 2-3  | Shift Register Rates and WC Latency Times                 | 2-13  |  |  |  |  |

| 3–1  | Pin List (Alphanumeric)                                   | 3–3   |  |  |  |  |

| 3-2  | Power and Ground Pin List                                 | 3–10  |  |  |  |  |

| 3–3  | Signal List (Alphanumeric)                                | 3–11  |  |  |  |  |

| 3-4  | Signal Descriptions (Alphanumeric)                        | 3–18  |  |  |  |  |

| 4-1  | 21174 Register Categories                                 | 4–1   |  |  |  |  |

| 4–2  | Hardware-Specific Register Address Map                    | 4–2   |  |  |  |  |

| 4-3  | General 21174 CSRs (Base = 87.4000.0000)                  | 4–2   |  |  |  |  |

| 4–4  | Diagnostic Registers (Base = 87.4000.0000)                | 4–3   |  |  |  |  |

| 4-5  | Performance Monitor Registers (Base = 87.4000.0000)       | 4–3   |  |  |  |  |

| 4–6  | Error Registers (Base = 87.4000.0000)                     | 4–3   |  |  |  |  |

| 4–7  | Memory Controller Registers                               | 4–4   |  |  |  |  |

| 4–8  | PCI Window Control Registers                              | 4–5   |  |  |  |  |

| 4–9  | Address Translation Registers                             | 4–6   |  |  |  |  |

| 4-10 | Miscellaneous Registers (Base Address = 87.8000.0000)     | 4–8   |  |  |  |  |

| 4-11 | Interrupt Control Registers (Base Address = 87.A000.0000) | 4–8   |  |  |  |  |

| 5–1  | Revision Control Register Fields                          | 5–2   |  |  |  |  |

| 5–2  | PCI Latency Register Fields                               | 5–3   |  |  |  |  |

| 5-3  | Control Register Fields                                   | 5–4   |  |  |  |  |

| 5-4  | Default PCI READ Prefetch Algorithm                       | 5–7   |  |  |  |  |

| 5-5  | Control Register 1 Fields                                 | 5–8   |  |  |  |  |

| 5–6  | Flash Control Register Fields                             | 5–9   |  |  |  |  |

| 5–7  | Hardware Address Extension Register (HAE_MEM) Fields      | 5–11  |  |  |  |  |

| 5–8  | PCI Address Mapping                                       | 5–12  |  |  |  |  |

| 5-9  | Hardware Address Extension Register (HAE_IO) Fields       | 5–13  |  |  |  |  |

| 5-10 | Configuration Type Register Fields                        | 5–13  |  |  |  |  |

| 5–11 | Diagnostic Control Register Fields                        | 5–14  |  |  |  |  |

| 5–12 | Diagnostic Check Register Fields                          | 5–15  |  |  |  |  |

| 5–13 | Performance Monitor Register Fields                       | 5–16  |  |  |  |  |

| 5–14 | Performance Monitor Control Register Fields               | 5–17  |  |  |  |  |

| 5–15 | PERF_MONITOR Register Low/High Select Field Codes         | 5–18  |  |  |  |  |

| 5–16 | Error Register Fields                                     | 5–20  |  |  |  |  |

| 5–17 | Status Register Fields                                    | 5–22  |  |  |  |  |

| 5–18 | Error Mask Register Fields                                |       |  |  |  |  |

| 5–19 | Syndrome Register Fields                                  | 5–25  |  |  |  |  |

| 5-20 | Memory Error Address Register Fields                      | 5–27  |  |  |  |  |

| 5–21 | Memory Error Status Register Fields                          | 5–28 |

|------|--------------------------------------------------------------|------|

| 5–22 | DATA_CYCLE_TYPE Codes                                        | 5–29 |

| 5–23 | SEQ_STATE Codes                                              | 5–30 |

| 5–24 | PCI Error Register 0 Fields.                                 | 5–34 |

| 5–25 | PCI Error Register 1 Fields.                                 | 5–36 |

| 5–26 | PCI Error Register 2 Fields.                                 | 5–37 |

| 5–27 | Memory Control Register Fields                               | 5–38 |

| 5–28 | DRAM_MODE Fields                                             | 5–40 |

| 5–29 | Memory Clock Mask Register Fields                            | 5–41 |

| 5–30 | MCMR Bit Definitions                                         | 5–42 |

| 5–31 | Global Timing Register Fields                                | 5–43 |

| 5–32 | Refresh Timing Register Fields                               | 5–44 |

| 5–33 | Row History Policy Mask Register Fields                      | 5–46 |

| 5–34 | Memory Control Debug Register 1 Fields                       | 5–46 |

| 5–35 | Memory Control Debug Register 2 Fields                       | 5–48 |

| 5–36 | Base Address Register Fields                                 | 5–49 |

| 5–37 | Bank Configuration Register Fields                           | 5–50 |

| 5–38 | Bank Timing Register Fields                                  | 5–51 |

| 5–39 | Cache Valid Map Register Fields                              | 5–53 |

| 5–40 | Scatter-Gather Translation Buffer Invalidate Register Fields | 5–54 |

| 5–41 | Window Base Register Fields                                  | 5–56 |

| 5–42 | Window Mask Register Fields                                  | 5–58 |

| 5–43 | W_MASK<31:20> Field                                          | 5–58 |

| 5–44 | PCI Address Translation — Scatter-Gather Mapping Disabled    | 5–58 |

| 5–45 | PCI Address Translation — Scatter-Gather Mapping Enabled     | 5–59 |

| 5–46 | Translated Base Registers Fields                             | 5–60 |

| 5–47 | Window DAC Base Register Fields                              | 5–62 |

| 5–48 | Lockable Translation Buffer Tag Register Fields              | 5–63 |

| 5–49 | Translation Buffer Tag Register Fields                       | 5–64 |

| 5–50 | Translation Buffer Page Register (TBm_PAGEn) Fields          | 5–66 |

| 5–51 | Clock Control Register Fields                                | 5–67 |

| 5–52 | Clock Status Register Fields                                 | 5-70 |

| 5–53 | Reset Register Fields                                        | 5-71 |

| 5–54 | Interrupt Request Register Fields                            | 5–73 |

| 5–55 | Interrupt Mask Register Fields                               | 5–74 |

| 5–56 | Interrupt High/Low Select Register Fields                    | 5–75 |

| 5–57 | Interrupt Routine Select Register Fields                     | 5–76 |

| 5–58 | General-Purpose Output Register Fields                       | 5–77 |

| 5–59 | Interrupt Configuration Register Fields                      | 5–78 |

| 5–60 | Clock Delay Values                                           | 5–79 |

| 5–61 | Clock Divisor Values                                         | 5-80 |

| 5–62 | Real-Time Counter Register Fields                            | 5-81 |

| 5–63 | Interrupt Time Register Fields                               | 5–82 |

| 5–64 | I2C Control Register Fields                          | 5–83 |

|------|------------------------------------------------------|------|

| 6–1  | Physical Address Map (Byte/Word Mode Disabled)       | 6–1  |

| 6–2  | Physical Address Map (Byte/Word Mode Enabled)        | 6–2  |

| 6–3  | 21164 Byte/Word Addressing                           | 6–14 |

| 6–4  | 21164 Byte/Word Translation Values                   | 6–14 |

| 6–5  | Int4_valid and 21164 Address Relationship            | 6–19 |

| 6–6  | PCI Memory Sparse-Space Read/Write Encodings         | 6-20 |

| 6–7  | PCI Address Mapping                                  | 6–21 |

| 6–8  | PCI Sparse I/O Space Read/Write Encodings            | 6-24 |

| 6–9  | CPU Address to IDSEL Conversion                      | 6–28 |

| 6–10 | PCI Configuration Space Read/Write Encodings         | 6–29 |

| 6–11 | Hardware and Miscellaneous Address Map               | 6–31 |

| 6–12 | PCI Target Window Mask Register Fields               | 6–33 |

| 6–13 | Direct-Mapped PCI Target Address Translation         | 6–37 |

| 6–14 | Scatter-Gather Mapped PCI Target Address Translation | 6–39 |

| 6–15 | PCI Window Power-Up Configuration                    | 6–45 |

| 7–1  | Absolute Maximum Electrical Ratings                  | 7–1  |

| 7–2  | DC Specifications                                    | 7–2  |

| 8–1  | Thermal Management Configurations for the 21174      | 8–4  |

| C-1  | Layer Construction                                   | C-3  |

| C-2  | System Clock Signals Layout Rules                    | C-4  |

| C-3  | Bcache Signal Layout Lengths                         | C-5  |

| C-4  | DRAM Clock Signal Layout Rules                       | C-6  |

| C-5  | PCI Clock Signal Layout Rules                        | C-6  |

| C-6  | Bcache Signal Layout Rules                           | C-7  |

# **Preface**

# **Purpose and Audience**

The DIGITAL Semiconductor 21174 Core Logic Chip Technical Reference Manual describes the operation of the DIGITAL Semiconductor 21174 core logic chip (also referred to as the 21174). This manual is for designers who use the 21174.

# **Manual Organization**

This manual contains the following chapters, appendixes, and an index.

- Chapter 1, Introduction, includes a general description of the 21174. It also provides an overview of the workstation configuration.

- Chapter 2, Internal Architecture, provides the physical layout of the 21174 and describes each of the input and output signals.

- Chapter 3, Pinout, provides the pin layout of the 21174 and describes each of the input and output signals.

- Chapter 4, Register Definitions, provides a complete list of the 21174 registers.

- Chapter 5, Register Descriptions, provides a complete bit description of the 21174 registers.

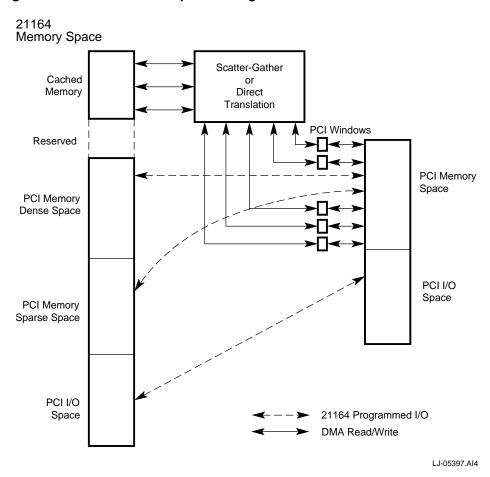

- Chapter 6, System Address Space, describes the organization of the system address space and shows the methods used to translate 21164 and PCI addresses.

- Chapter 7, Electrical Specifications, lists the dc electrical specifications for the 21174.

- Chapter 8, Mechanical and Thermal Specifications, lists and illustrates the mechanical and thermal specifications of the 21174.

- Appendix A, 21174 DMA Page Boundary Solution, provides the files and the code necessary to manage PCI DMA reads that cross 8K page boundaries.

- Appendix B, 21174 DMA Lock Solution, explains how to manage inappropriate LOCK commands issued by the 21164 to the CMD bus.

- Appendix C, AlphaPC 164LX Layout Design Rules, contains the module design layout rules.

- Appendix D, Support, Products, and Documentation, contains information about technical support and ordering information.

# **Conventions**

This section describes the abbreviation and notation conventions used throughout this manual.

### **Bit Notation**

Multiple bit fields are shown as extents (see Extents).

## Caution

Cautions indicate potential damage to equipment or loss of data.

### **Data Units**

Table 1 defines the data unit terminology used throughout this manual.

Table 1 Data Units

| Term     | Words | Bytes | Bits | Other                                                                                                                                                    |

|----------|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte     | 1     | _     | 8    | _                                                                                                                                                        |

| Word     | 1     | 2     | 16   | _                                                                                                                                                        |

| Tribyte  | _     | 3     | 24   | _                                                                                                                                                        |

| Longword | 2     | 4     | 32   | _                                                                                                                                                        |

| Quadword | 4     | 8     | 64   | _                                                                                                                                                        |

| Octaword | 8     | 16    | 128  | Single read fill; that is, the cache space that can be filled in a single read access. It takes two read accesses to fill one Bcache line (see Hexword). |

| Hexword  | 16    | 32    | 256  | Cache block, cache line. The space allocated to a single cache block.                                                                                    |

#### **Extents**

Extents are specified by a pair of numbers in angle brackets (<>) separated by a colon (:) and are inclusive. For example, bits <7:3> specifies an extent including bits 7, 6, 5, 4, and 3.

## **Logic Levels**

The values 1, 0, and X are used throughout the manual. A 1 signifies a logic high, a 0 signifies a logic low, and an X signifies a don't care (1 or 0) which can be determined by the system designer.

#### **Must Be Zero**

Fields specified as must be zero (MBZ) must never be filled by software with a nonzero value. If the processor encounters a nonzero value in a field specified as MBZ, a reserved operand exception occurs.

#### **Note**

Notes emphasize particular information.

## Numbering

All numbers are decimal or hexadecimal unless otherwise specified. In cases of ambiguity, a subscript indicates the radix of nondecimal numbers. For example, 19 is decimal, but  $19_{16}$  and 19A are hexadecimal.

## **Processor Chip Type**

All references to the 21164 microprocessor specifically refer to the version of the DIGITAL Semiconductor 21164 in 0.35- $\mu$ m CMOS and to the DIGITAL Semiconductor 21164PC in 0.35- $\mu$ m CMOS.

### Ranges

Ranges are specified by a pair of numbers separated by two periods (..) and are inclusive. For example, a range of integers 1..4 includes the integers 1, 2, 3, and 4.

## **Register and Memory Figures**

Register figures have bit and field position numbering starting at the right (low-order) and increasing to the left (high-order). Memory figures have addresses starting at the top and increasing toward the bottom.

All shaded bits and bit fields in the figures are reserved, and software drivers should write only 0 to these bits and bit fields.

Register figures and tabulated descriptions have a mnemonic that indicates the bit or field characteristic as described in Table 2.

**Table 2 Register Field Notation**

| g        |                                                                                                                                                                                                                                                                            |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Notation | Description                                                                                                                                                                                                                                                                |  |  |

| RW       | A read-write bit or field. The value can be read and written by software, microcode, or hardware.                                                                                                                                                                          |  |  |

| RO       | A read-only bit or field. The value can be read by software, microcode, or hardware. The bit is written by hardware. Software or microcode write operations to this bit are ignored.                                                                                       |  |  |

| WO       | A write-only bit. The value can be written by software and microcode. The bit is read by hardware. Read operations to this bit by software or microcode return an UNPREDICTABLE result.                                                                                    |  |  |

| WZ       | A write-only bit or field. The value can be written by software or microcode. The bit is read by hardware. Read operations to this bit by software or microcode return a zero.                                                                                             |  |  |

| WC       | A write-to-clear bit. The value can be read by software or microcode. Software or microcode write operations with a 1 to this bit cause the bit to be cleared by hardware. Software or microcode write operations with a 0 to this bit do not modify the state of the bit. |  |  |

| RC       | A read-to-clear field. The bit is written by hardware and remains unchanged until the bit is read. The bit can be read by software or microcode, at which point hardware can write a new value into the field.                                                             |  |  |

Other register fields that are unnamed may be labeled as specified in Table 3.

**Table 3 Unnamed Register Field Notation**

| Notation | Description                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | A 0 in a bit position indicates a register bit that is read as a 0 and is ignored on a write operation.                                                    |

| 1        | A 1 in a bit position indicates a register bit that is read as a 1 and is ignored on a write operation.                                                    |

| X        | An x in a bit position indicates a register bit that does not exist in hardware. The value is UNPREDICTABLE when read and is ignored on a write operation. |

#### **Should Be Zero**

Fields specified as should be zero (SBZ) should be filled by software with a zero value. These fields may be used at some future time. Nonzero values in SBZ fields produce UNPREDICTABLE results.

### Signal Name References

Signal names are printed in boldface, lowercase type. Mixed-case and uppercase signal naming conventions are ignored. These two examples illustrate the conventions used in this document:

- MEM\_WE\_L[1] is shown as mem\_we\_l<1>

- TEST MODE[1] is shown as test mode<1>

#### **UNPREDICTABLE and UNDEFINED Definitions**

Results specified as UNPREDICTABLE may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. Software can never depend on results specified as UNPREDICTABLE.

Operations specified as UNDEFINED may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. The operation may vary from nothing to stopping system operation. UNDEFINED operations must not cause the processor to hang, that is, reach a state from which there is no transition to a normal state where the machine can execute instructions.

Note the distinction between results and operations. Nonprivileged software cannot invoke UNDEFINED operations.

# Warning

Warnings provide information to prevent personal injury.

# Introduction

The DIGITAL Semiconductor 21174 core logic chip (also referred to as the 21174) is a single-chip core logic PCI-to-21164 interface for low-cost workstations. It provides an inexpensive memory, cache, and PCI controller for uniprocessor workstations. The 21174 may be used with 21164PC devices and with 21164 devices that support a clock frequency equal to or greater than 400 MHz. These types of devices are referred to as 21164 in this manual.

## 1.1 21174 Features

The 21174 has the following features:

- Synchronous dynamic RAM (DRAM) memory controller

- Supports optional Bcache (level 3 cache)

- Supports 64-bit PCI at 33 MHz

- 64 interrupts through external shift register

- 32 general-purpose inputs through external shift register

- 32 general-purpose outputs through external shift register

- 3.3-V design

- Quadword ECC support, longword parity, or no parity on system and memory data buses

- Onchip phase-locked loop (PLL)

- Direct attachment of flash ROM

- Startup from flash ROM

- Compact design, complete interface in single 474-pin ball grid array (BGA)

# 21174 System Configuration

- 1000 MB/s peak memory bandwidth

- Glueless workstation memory controller

# 1.2 21174 System Configuration

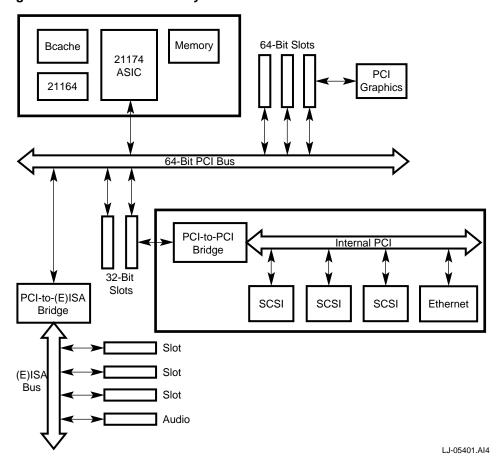

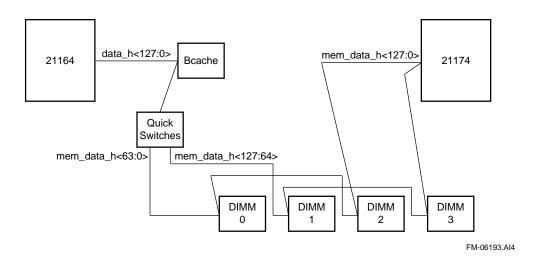

Figure 1–1 shows the 21174 used in a system configuration.

Figure 1-1 System Configuration

See Appendix C for additional details on designing a system using two DIMM pairs. Appendix C also contains key module layout design rules. It is crucial that these rules are followed when designing a system.

# Internal Architecture

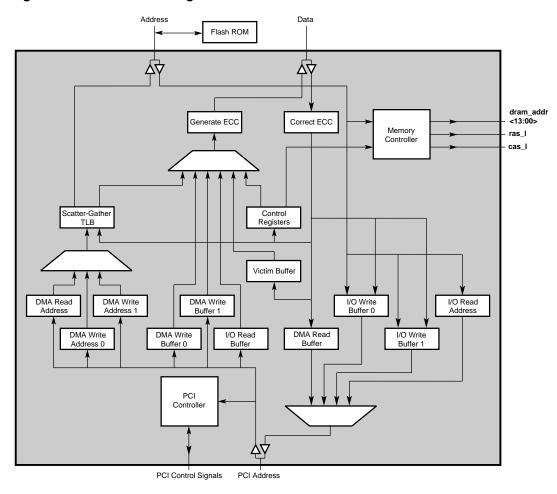

The 21174 provides an interface between three units — memory, the PCI bus, and the 21164 (along with flash ROM). Figure 2–1 shows the internal components of the 21174 and the three internal units: memory controller, PCI interface, and the interface to the 21164 flash ROM.

# 2.1 Memory Controller

The 21174 memory controller provides clocks, data, address, and control to the memory unit. When power is turned on, the memory controller gathers information from the memory banks, and then uses that information to initialize and configure the memory unit.

## 2.1.1 Memory Sequencers

The memory sequencer permits up to two partially overlapping memory transactions to be active at any given time. The sequencer is internally implemented in two parts; the master sequencer and the data transfer machine. The master sequencer initiates all memory operations and I/O operations. It generates all control signal timings for the SDRAMs. When a memory operation has progressed to the point where a column access has started, the master sequencer hands off the transaction to the data transfer machine. The data transfer machine controls the four data cycles that complete the transaction. In most cases, the master sequencer is ready to start a new transaction as soon as the old transaction has been handed off to the data transfer machine.

Figure 2-1 21174 Block Diagram

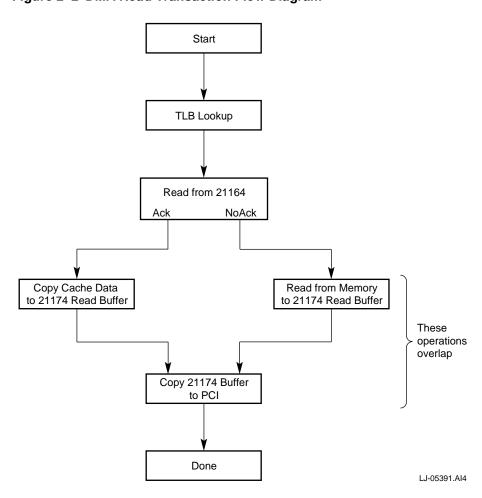

#### 2.1.2 DMA Read Transaction

A DMA read transaction consists of an optional scatter-gather translation lookaside buffer (TLB) lookup (and TLB refill, if needed), followed by a probe transaction to the 21164, followed by either a cache read from 21164 or a read from the memory. Figure 2–2 shows a flow diagram of a DMA read transaction. The length of the DMA read transaction is determined by the prefetch logic associated with the scattergather TLB.

If the scatter-gather lookup misses in the TLB, an additional cache probe, and possibly a memory read transaction, must be performed to fill the TLB before completing the main probe and memory transaction. The DMA read address is also compared to the victim buffer addresses. If there is a victim buffer hit, data from the victim buffer is substituted for the memory read transaction data.

## 2.1.2.1 PCI DMA Page Boundary Problem

PCI DMA reads that attempt to cross 8K page boundaries cause data corruption problems.

See Appendix A for the DMA page boundary solution.

Figure 2–2 DMA Read Transaction Flow Diagram

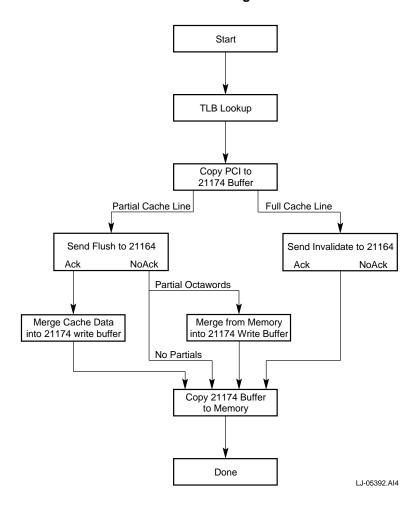

#### 2.1.3 DMA Write Transaction

A DMA write transaction consists of an optional scatter-gather TLB lookup (and TLB refill, if needed), followed by a flush transaction to the 21164, followed by a write to the memory. Figure 2–3 shows a flow diagram of a DMA write transaction.

If the scatter-gather lookup misses in the TLB, an additional cache probe, and possibly a memory read, must be performed to fill the TLB before completing the main probe and memory transaction.

The physical DMA address is also compared to the victim buffer addresses. If there is a victim buffer hit, the victim buffer data is merged with the write buffer before the write is performed, and the victim buffer is invalidated.

Figure 2-3 DMA Write Transaction Flow Diagram

#### 2.1.4 21174 DMA Lock Problem

The 21164 sometimes issues LOCK commands on the CMD bus. The 21174 treats the LOCK command as a no-op command and goes back to idle. This does not actually clear the LOCK command. Thus, the process repeats indefinitely, blocking DMA requests that may be waiting for service.

See Appendix B for the solution to this problem.

## 2.1.5 Minimum Memory Activation Period

Several cases where the memory controller activates the memory arrays but does not perform a read or write operation are described here:

- If the victim buffer is hit during a 21164 read transaction, the memory controller performs a complete memory read operation and then discards the data before taking the data from the victim buffer.

- If the cache is hit during a DMA read transaction, the memory controller may have activated the memory arrays but does not perform a read operation. The 21164 takes the data from the cache while the memory controller completes the cache read cycles before returning to the idle state. In the worst case, the following state sequence occurs.

| State              | SELECT State          | Number of Cycles |

|--------------------|-----------------------|------------------|

| DMA_RD_PROBE       | SELECT is asserted.   | n cycles         |

| DMA_RD_SCACHE_DATA | SELECT is deasserted. | 2 cycles         |

| DMA_RD_CACHE_DATA  | SELECT is deasserted. | 4 cycles         |

| IDLE               | _                     | _                |

This state sequence implies that the memory arrays will be activated for a minimum of 6 (5) cycles, because the soonest that a new SELECT can occur is during the IDLE cycle.

The DMA\_RD\_PROBE state deasserts SELECT when the next state is DMA\_RD\_SCACHE\_DATA or DMA\_RD\_CACHE\_DATA. This adds one state, which provides an additional margin, extending the minimum guarantee for the activated memory arrays to 7 (6) cycles. This is enough time for all currently available or proposed SDRAMs.

## **Memory Banks**

During a DMA write transaction, even if there is a cache hit or victim buffer hit, there is a write-back to the selected memory location, so the memory arrays cannot become stranded in the activated state.

# 2.2 Memory Banks

The 21174 memory controller supports up to two banks, i.e. four DIMM slots, of synchronous DRAM memory. Each bank can have two sub-banks. The memory banks may be of different sizes and speeds, but the two sub-banks within a bank must be identical.

See Figure 1–1 for a typical system configuration.

The 21174 reads the I<sup>2</sup>C control register (see Section 5.9.9), by way of the I<sup>2</sup>C bus, to check for the absence or presence of memory DIMMs. Startup code will read the information from each DIMM. Each DIMM must contain the proper I<sup>2</sup>C ROM.

#### 2.2.1 Refresh

The operation of memory refresh is controlled by using the refresh timing register. All banks of memory are refreshed simultaneously.

# 2.2.2 Error Checking and Correction

The 21174 operates in one of two software selectable modes — ECC or PCA56 longword parity. Use PYXIS\_CTRL[ECC\_CHK\_EN] to enable ECC checking or use PYXIS CTRL1[LW PAR MODE] to enable PCA56 longword parity mode.

Initialization firmware must check the memory banks and the 21164 to determine whether parity or ECC bits are present in the memory and whether the 21164 will support ECC. The firmware then establishes the state of the error checking and error code generation based on this criteria. If the memory does not provide ECC/parity bits, then all memory error checking should be turned off.

If the 21174 is operated with error checking enabled, the memory should be initialized by firmware to contain good ECC or parity in all locations.

If the 21174 is operating in ECC mode and an ECC error occurs on a DMA read transaction or I/O write transaction, the ECC error is corrected. If the ECC error is not correctable, the DMA read or I/O write transaction will not complete. In either case, appropriate error status bits are set and the 21174 error interrupt is asserted if error reporting is enabled. The interrupt service routine must clear the error status bits to deassert the error interrupt.

## **Memory Banks**

If a parity error is detected on I/O read transaction data or DMA write transaction data, the operation will complete. The appropriate error bits are set and the error interrupt is asserted if error reporting is enabled.

#### 2.2.3 DRAM Initialization

After power-up, the memory must be activated. The activation requires at least two refresh cycles before and after writing data (in hexadecimal) from the memory control register to the DIMMs. The algorithm is:

- 1. Write  $634_{16}$  to the global timing register.

- 2. Write 80E0 to the refresh timing register (refresh width = 6, refresh interval = 5, and force refresh asserted).

- 3. Wait approximately 300 ns.

- 4. Write 80E0 to the refresh timing register (refresh width = 6, refresh interval = 5, and force refresh asserted).

- 5. Wait approximately 300 ns.

- 6. Write 3A0001 to the memory control register (3A is memory specific and the 1 is mode register set).

- 7. Write 80E0 to the refresh timing register (refresh width = 6, refresh interval = 5, and force refresh asserted).

- 8. Wait approximately 300 ns.

- 9. Write 80E0 to the refresh timing register (refresh width = 6, refresh interval = 5, and force refresh asserted).

- 10. Wait approximately 300 ns.

Executing this algorithm wakes up memory and sets the DRAM mode registers. This sequence configures the memory SDRAMs to the burst length, wrap type, and latency mode. This sequence is required by the SDRAMs and is not part of the system memory configuration sequence. Prior to accessing the memory, ensure that the memory is configured correctly, that PCA56 longword parity mode or ECC mode is set up properly, and that all of memory is written to initialize the memory error detection fields prior to enabling error checking. Write to memory only if error checking is to be performed.

Note:

The SROM code is responsible for setting up the memory system. In most cases the memory system will be initialized prior to transferring control out of the initialization code.

#### 2.3 PCI Interface

The PCI interface is 64 bits wide and supports operation at up to 33 MHz. Operation of the PCI is always synchronous to sys\_clk. The PCI interface can be operated at a clock frequency ratio of 2:1 relative to the 21164 sys\_clk frequency. The operating frequencies are listed in Table 2–1.

Table 2-1 PCI Operating Frequencies

| CPU<br>Frequency | sys_clk<br>Ratio | sys_clk<br>Frequency | sys_clk Cycle<br>Time | PCI<br>Frequency | PCI/sys_clk<br>Ratio |

|------------------|------------------|----------------------|-----------------------|------------------|----------------------|

| 466 MHz          | 7                | 66.0 MHz             | 15.00 ns              | 33.0 MHz         | 2:1                  |

| 533 MHz          | 8                | 66.0 MHz             | 15.00 ns              | 33.0 MHz         | 2:1                  |

| 600 MHz          | 9                | 66.0 MHz             | 15.00 ns              | 33.0 MHz         | 2:1                  |

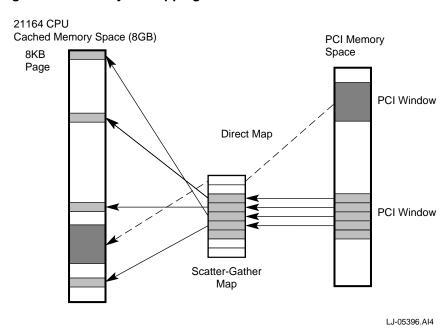

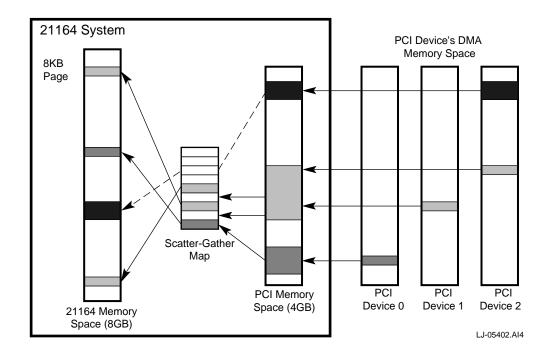

### 2.3.1 Scatter-Gather Map

The TLB provides eight scatter-gather map entries. Scatter-gather operation is enabled by setting the appropriate enable bit in the window base registers.

#### 2.3.2 DMA Read Prefetch

The scatter-gather map TLB entries in the 21174 each contain a prefetch length field. The prefetch length field indicates the total number of 128-bit memory cycles to be fetched to satisfy the request. The prefetcher always fetches exactly the number of cycles specified in the prefetch length field. When the data is exhausted, the 21174 disconnects.

When a TLB entry is first loaded, the prefetch length is set to the value given in the appropriate read type field in the control register (PYXIS CTRL). If the appropriate USE\_HISTORY bit is set and the initiator disconnects without accepting all available prefetched data, the prefetch length is set to the number of memory cycles needed to supply the data transferred. During subsequent write transactions, the previous length is used to determine the prefetch length. See the description of the control register (PYXIS\_CTRL) in Section 5.1.3.

#### 2.3.3 DMA Write Buffer

A 2-entry write buffer is provided for DMA write data. Each entry is 64 bytes in length. When both buffers are in use, 21174 issues a retry response to DMA write transactions.

#### **PCI** Interface

At the beginning of a PCI DMA write transaction, an unused write buffer is allocated for the transaction. The write data is aligned within the write buffer based on the low-order bits of the address. Address mask information is updated during the transaction. If the transaction reaches the end of the cache line, the 21174 disconnects. After a write buffer entry has been written, the 21174 schedules a memory write transaction or a memory read-modify-write transaction, depending on the state of the mask bits in the write buffer, to copy the data to memory.

When a PCI read transaction is initiated from the 21164, the 21174 ensures that the DMA write buffers are flushed to memory before returning the read data to the 21164.

### 2.3.4 DMA Write Buffer Merging

During DMA write transactions, byte mask information is received from the PCI bus. Depending on the alignment of the starting address and the state of the byte masks, it may be necessary to read quadwords from memory and merge bytes into the DMA quadwords before writing the DMA data to memory.

After a DMA write buffer in the 21164 is filled, the 21174 determines how many memory cycles are needed to complete the write transaction. The 21174 also determines if it is necessary to merge data within any quadword or if an empty quadword exists between quadwords that contain data. If either condition exists, a read-modifywrite transaction sequence is scheduled instead of the simple DMA write transaction sequence performed for a normal aligned DMA. The read-modify-write transaction sequence is performed in the following order:

- 1. All quadwords of the DMA transaction are read from memory across d<127:0> into the 21174 chip. The bytes not selected by the DMA transaction are merged into the DMA write buffers.

- 2. All quadwords of the DMA transaction are written back to memory.

#### 2.3.5 I/O Write Buffer

A 2-entry write buffer is provided for PCI write transactions originated from the 21164. Consecutive entries may be merged under optimal circumstances.

#### 2.3.6 Configuration Cycles and Special Cycles

Configuration cycles and special cycles are generated in compliance with the PCI Local Bus Specification, Version 2.1. See Sections 6.9 and 6.10 for more information.

#### Flash ROM Interface

## 2.4 Flash ROM Interface

A flash ROM can be directly attached to the addr<39:4> signal lines. The address and data bits of the flash ROM are connected to the addr<39:4> pins as shown in Table 2–2.

Table 2-2 Flash ROM Pin Assignment

| 21174 Pin | Flash ROM Pin | 21174 Pin  | Flash ROM Pin |

|-----------|---------------|------------|---------------|

| addr<39>  | OE            | addr<16>   | A<3>          |

| addr<31>  | A<18>         | addr<15>   | A<2>          |

| addr<30>  | A<17>         | addr<14>   | A<1>          |

| addr<29>  | A<16>         | addr<13>   | A<0>          |

| addr<28>  | A<15>         | addr<12>   | A < B >       |

| addr<27>  | A<14>         | addr<11>   | D<7>          |

| addr<26>  | A<13>         | addr<10>   | D<6>          |

| addr<25>  | A<12>         | addr<9>    | D<5>          |

| addr<24>  | A<11>         | addr<8>    | D<4>          |

| addr<23>  | A<10>         | addr<7>    | D<3>          |

| addr<22>  | A<9>          | addr<6>    | D<2>          |

| addr<21>  | A<8>          | addr<5>    | D<1>          |

| addr<20>  | A<7>          | addr<4>    | D<0>          |

| addr<19>  | A<6>          | flash_ce_l | ce_1          |

| addr<18>  | A<5>          | flash_we_l | we_l          |

| addr<17>  | A<4>          | _          | _             |

The flash ROM can be read and written through the address range selected in the flash ROM control register. After reset, the flash ROM is at location 0. The 21174 supports cache fills and noncacheable reads from the flash ROM. For example, the 21174 will perform multiple read transactions to the flash ROM to assemble full octawords. The processor can start executing directly from the flash ROM if the 21164 is configured to start from cache misses rather than from SROM.

#### **Auto DACK**

For flash ROMs smaller than 64MB, the high-order address bits can be left unconnected. This results in aliasing of the flash ROM throughout the flash ROM address space. It is also possible to attach multiple flash ROMs, or other devices, using the control bits and high-order address bits to drive a decoder. In this case, buffers may be needed to limit the loading for each signal within addr<39:4>.

If the flash ROM is accessed through cache fills (for example, through one of the windows in cacheable space), an unwanted parity error on the address bus (addr<39:4> and cmd<2:0>) may be generated unless the 21164 Bcache control register bit, BC\_CONTROL[DIS\_SYS\_PAR], is set. Setting the DIS\_SYS\_PAR bit will disable parity errors during any type of flash ROM transactions. Unwanted parity errors may also be inhibited by setting BC\_CONTROL[EI\_DIS\_ERR]. The EI\_DIS\_ERR bit is initialized to 1 during 21164 reset, so in the 21164 initial state, no unwanted parity errors will be generated.

On a system with a Bchache, if a private cache write is overlapped with the beginning of a fill from the flash ROM, with the fill approximately asserted on the second cycle of the private write, the system will appear to hang. This probably affects cacheable flash ROM fills and has only been seen on an I-stream miss at the end of a flash-to-memory copy. A workaround has been incorporated into the SROM code to add additional timing that prevents the system from hanging. I-stream and D-stream fills from cache should be limited to SROM operation. All other accesses to the flash ROM should be done using the I/O space assigned to flash memory space.

#### 2.5 Auto DACK

The 21164 supports an "Auto DACK" feature to accelerate data bus transfers. When this feature is enabled by setting the AUTO\_DACK bit in the 21164 BC\_CONTROL register, the 21164 assumes that the final two DACKs of a data transfer are contiguous. The 21174 supports this mode of operation.

# 2.6 Dummy Memory

A dummy memory block is provided to facilitate flushing of 21164 Scache and Bcache. Read transactions to this 4-GB block of dummy memory region causes a value of 0 to be returned. Write transactions to this memory region result in nonexistent memory traps. The dummy memory region is the last 4GB of cached memory address space starting at E.0000.0000.

### Interrupts

The dummy memory region can be effectively used to implement a small memory area at power-up, using the processor's Dcache (level 1) and Scache (level 2). If the 21164 is set up to access memory within the dummy area, fills will be served by the dummy area, but after the fill, the cache will work properly to serve those memory addresses. Use only a memory area that will fit within the Dcache and Scache, because a victim ejection will cause a machine check. This same technique can be used to emulate a much larger memory using the optional Bcache (level 3). It is also possible to use the flash ROM address spaces to emulate memory, but the fills from this space are much slower because they require sequential flash ROM transactions. In either case, avoid sharing cache address space with the instruction stream to prevent inadvertent victim ejections.

# 2.7 Interrupts

Interrupts and general-purpose inputs are acquired through a free-running 64-bit external shift register. Typically, the shift register is implemented with one or more 74HC165 chips. The shift register does not need to be fully implemented if fewer than 64 bits of interrupts and general-purpose inputs are needed. The int\_sr\_load\_l signal is asserted low to load the interrupts into the shift register. The int sr clk signal clocks the shift register contents into the 21174 through the **int\_sr\_in** pin. The shift register clock rate depends on the CPU speed. See Table 2–3 to determine the shift register rate and latency time. If fewer than 64 inputs are needed, the interrupt latency can be reduced by writing a smaller value into the IRQ\_COUNT field of the INT\_CNFG register.

Table 2-3 Shift Register Rates and WC Latency Times

| CPU Speed | System Clock Rate | Shift Register Rate | WC Latency          |

|-----------|-------------------|---------------------|---------------------|

| 466 MHz   | 66.67 MHz         | 16.67 MHz           | 3.84 usec (approx.) |

| 533 MHz   | 66.67 MHz         | 16.67 MHz           | 3.84 usec (approx.) |

| 600 MHz   | 66.67 MHz         | 16.67 MHz           | 3.84 usec (approx.) |

The normal active state of interrupts is active low. The INT\_HILO register is provided to allow for devices that are active high, such as the 82378 ISA bridge. The register provides for eight devices that can be made active high. Setting a bit in this register causes the active state of the interrupt to be changed from active low to active high.

## **General-Purpose Inputs and Outputs**

The state of each interrupt or input can be read through the interrupt request register. The state of the interrupts will persist in the interrupt register for up to 3  $\mu$ sec after the interrupt has been deasserted at the shift register input. If the interrupt bit in the interrupt request register is not promptly cleared, a second interrupt might be taken before the shift register scans the deasserted value into the interrupt request register. For this reason, interrupts latched in the interrupt request register can be reset individually by writing a 1 to the bit to be cleared. This immediately clears the bit to avoid taking a second interrupt. It is also acceptable to write 1 to all interrupt bits within the interrupt request register.

The interrupt mask register provides individual mask bits for each interrupt. The bits used for general-purpose inputs should be masked using this register.

In normal operation, all external interrupt sources are routed to **irq<1>\_h** on the 21164. In some instances, it may be necessary to route the sources to **irq<0>\_h** or **irq<3:2>\_h**. The 21174 provides for eight external interrupt sources that can be routed to different 21164 interrupt request lines. See the description of the interrupt routine select register (INT\_ROUTE) in Section 5.9.4 for a description of this function.

# 2.8 General-Purpose Inputs and Outputs

General-purpose inputs can be configured using the interrupt's external shift register. When the interrupt's external shift register is used for general-purpose inputs, the interrupt enable bits should be deasserted.

General-purpose outputs can be implemented with one or more 74HC595 chips. The contents of the general-purpose output register are continuously transferred to the shift register. The worst case delay for output posting is approximately 3 µsec, or less if the IRQ\_COUNT field of the INT\_CNFG register is programmed to reduce the length of the shift register cycle time.

# 2.9 Programmed 21164 Reset

The 21164 processor can be restarted by setting the DO\_RESET in the power control register. This is usually done to change the 21164 frequency or the **sys\_clk** divider ratio. The **sys\_clk** divider ratio can be set in the CSR\_CLOCK\_DIVIDE and CSR\_PCLK\_DIVIDE fields of the clock control register. While **dc\_ok** is asserted, the initial value for this field is loaded from pull-up and pull-down resistors attached to the pins. This field can be written under program control, and the new value is used during any subsequent 21164 reset.

The duration of a programmed 21164 reset can be controlled by writing to the RESET PULSE WIDTH field in the power-down timing register.

#### 2.10 Clock

This section explains the internal clock PLL and the DRAM clock aligner.

#### 2.10.1 Clock PLL

An onchip PLL generates an internal clock at two times the sys\_clk rate. This clock is used to derive all other clocks. The fast clock is divided again by two or three to make a sys\_clk replica clock that is used to clock the internal 21174 logic. The fast clock is divided by 4 to generate the PCI clocks.

#### 2.10.2 DRAM Clock Aligner

A precision clock aligner generates clocks for the SDRAMs. The clock aligner allows the module designer to position the external clocks accurately within the overall clock cycle to maximize the margins for setup and hold times for the various system components.